A TSMC está a caminho de expandir sua capacidade de embalagem avançada de chip on wafer on substrato (CoWoS) em quase duas vezes até o final de 2024, mas mesmo assim a Nvidia consumirá metade da capacidade que a fundição deve ter, de acordo com o DigiTimes .

A TSMC supostamente pretende expandir sua capacidade CoWoS de 8.000 wafers por mês hoje para 11.000 wafers por mês até o final do ano e, em seguida, para cerca de 20.000 até o final de 2024. Mas parece que mesmo assim a Nvidia usará cerca de metade do capacidade que a TSMC terá, afirma o DigiTimes , citando fontes familiarizadas com o assunto. Enquanto isso, a AMD também está tentando reservar capacidade CoWoS adicional para o próximo ano.

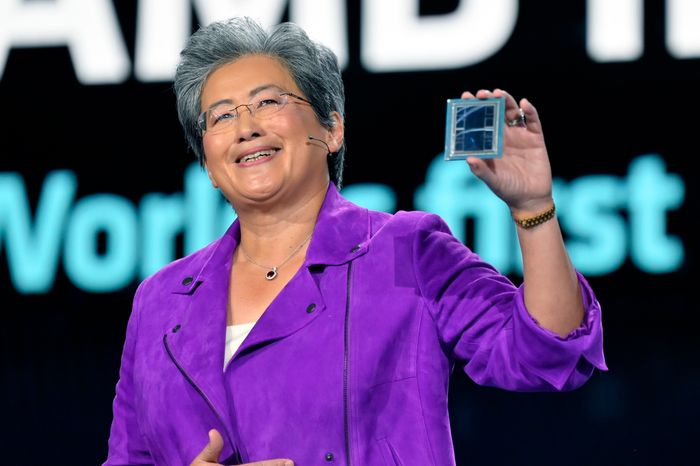

Megatendências como 5G, inteligência artificial (IA) e computação de alto desempenho (HPC) estão impulsionando a adoção de designs multichiplet altamente complexos, como o Instinct MI300 da AMD ou o H100 da Nvidia . É amplamente considerado que a Nvidia é a principal beneficiária da crescente demanda por GPUs de computação vinculadas à IA e que controla mais de 90% das remessas de GPU de computação para novas implantações. Como resultado, a TSMC está lutando para atender à demanda por suas soluções avançadas de embalagem CoWoS.

Atualmente, a TSMC tem capacidade para processar cerca de 8.000 wafers CoWoS por mês. Entre elas, a Nvidia e a AMD utilizam cerca de 70% a 80% dessa capacidade, tornando-as as usuárias dominantes dessa tecnologia. Depois deles, a Broadcom surge como o terceiro maior usuário, respondendo por cerca de 10% da capacidade de processamento de wafer CoWoS disponível. A capacidade restante é distribuída entre outros 20 projetistas de chips fabless.

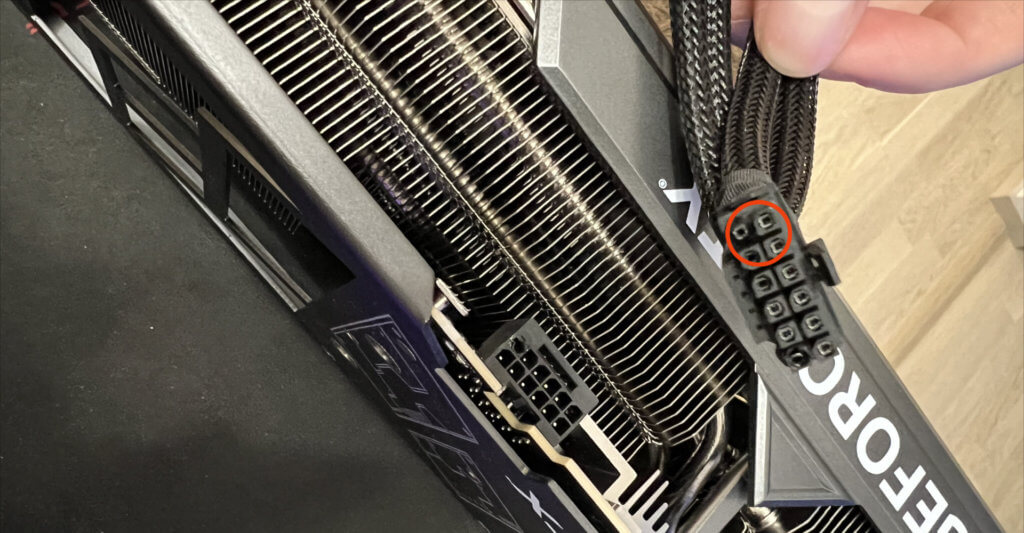

Os equipamentos de embalagem para CoWoS e outras tecnologias avançadas de embalagem exigem ferramentas de produção especializadas e têm prazos de entrega entre três e seis meses. Isso significa que a capacidade da TSMC de expandir rapidamente sua capacidade de CoWoS é limitada.

Na semana passada, a TSMC abriu sua instalação Advanced Backend Fab 6 , que deve expandir sua capacidade avançada de empacotamento tanto para suas tecnologias SoIC (CoW, WoW) de empilhamento 3D de front-end quanto para métodos de empacotamento 3D de back-end (InFO, CoWoS), mas por enquanto o fab está pronto para SoIC. O Advanced Backend Fab 6 tem a capacidade de processar cerca de um milhão de wafers de 300 mm por ano e realizar mais de 10 milhões de horas de testes anualmente, com espaço de sala limpa maior do que os espaços de sala limpa combinados de todas as outras instalações avançadas de embalagem da TSMC.

Entre os recursos mais impressionantes do Advanced Backend Fab 6 está o extenso sistema de manuseio de materiais automatizado inteligente cinco em um. O sistema controla o fluxo de produção e detecta defeitos instantaneamente, aumentando o rendimento. Isso é crucial para montagens complexas de vários chiplets como o MI300 da AMD, pois os defeitos de embalagem tornam imediatamente todos os chiplets inutilizáveis, levando a perdas significativas. Com recursos de processamento de dados 500 vezes mais rápidos que a média, a instalação pode manter registros de produção abrangentes e rastrear cada matriz que processa.

A Nvidia usa CoWoS para suas bem-sucedidas GPUs de computação A100, A30, A800, H100 e H800. O Instinct MI100 da AMD, o Instinct MI200/MI200/MI250X e o futuro Instinct MI300 também usam CoWoS.